Semiconductor Technology Offers Exciting Possibilities

This file type includes high resolution graphics and schematics when applicable.

In an ideal world, the latest devices would come equipped with compact, power-efficient, and ultra-connected supercomputers in a single chip. This one-stop-shop solution seems to be the goal of semiconductor companies and foundries alike. The latest integrated-circuit (IC) technologies are looking to integrate analog, digital, and RF components on the same chip. By doing so, they could more easily cater to the growing demand for commercial and military portable electronics while offering “big data” capability.

Related Articles

• SoCs Bring High-End RF Devices From Lab To Sofa

• LNA Includes Bypass Protection

• Module Boosts WLAN Signals

To enable such features, however, these devices must implement the necessary hardware in a compact and power-efficient way. Many developed and newer technologies have been highlighted as solutions to this problem. For example, Fin field-effect-transistors-on-bulk (FinFETson-bulk), fully depleted silicon-on-insulator gallium arsenide (FDSOI GaAs), and FinFET-on-SOI are being considered by big players like GlobalFoundries, IBM, Intel, ST, Soitec, and many others. Of course, there are many manufacturing, cost, supply, and market factors that need to be detailed for engineers and companies to invest in a certain technology. First, let us consider the different MOSFET-based technologies.

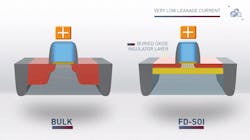

Fully depleted MOSFET channel techniques offer a solution to the increased source-to-drain leakage caused by decreased channel size. Shrinking the channel size enables smaller transistor typologies, but increases the effects of leakage, parasitics, and the need for advanced fabrication techniques. High-performing RF technologies require the best of both worlds. If a MOSFET is designed to be fully depleted in the off state, the source-to-drain leakage will be reduced significantly enough to enable RF operation. The most commonly accepted techniques currently being explored are FinFET or SOI techniques (Fig. 1).

FDSOI is a CMOS integrated technology that uses a highly resistive substrate—specified to be above 1000 Ω/cm—supporting a thin layer of silicon. This process adds some fabrication steps in terms of necessary development, but enables high-frequency capability by limiting loss through the substrate. FinFETs solve this leakage/parasitic problem by utilizing thin silicon fins, which project from the wafer for the MOSFET channel. FinFET technology can be adapted to either bulk or an SOI substrate.

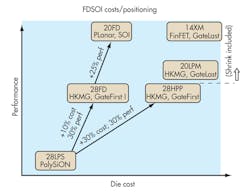

The benefit of FDSOI over bulk is one of decreased junction capacitance, although cost is a factor here (Figs. 2 and 3). Up-front costs aren’t always the leading factor—especially in the case of RF technologies. The application and end device in which the RF technology will be implemented could have significant influencing factors on the viability of a technology. Another major concern is the availability of high-quality passive components that can meet the demands of current RF technology in very small sizes. With backing from companies such as Soitec, MagnaChip, GlobalFoundries, Peregrine, Apple, IBM, Altis, Qualcomm, TowerJazz, Skyworks, STMicroelectronics, and others, the choice for the next push of RF technology development appears to be FDSOI.

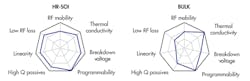

The development of FDSOI technologies could very much impact the well-entrenched use of GaAs, which has played significantly in the commercial as well as military markets. Generally, GaAs offers very high RF mobility and a high breakdown voltage. Such characteristics lead to low RF losses, high linearity, and low-noise operation. Millimeter wave-frequency applications can take advantage of these factors. But the demands for some commercial markets involve increased integration.

For low-power RF solutions, GaAs faces a significant limitation of GaAs: its lack of digital integration solutions. This failing is particularly felt in the handheld and portable device markets, whichare seeking a single system-on-a-chip (SoC) solution. The test and measurement equipment markets also are seeing demand for heightened integration of analog, digital, and RF technologies. As a result, a lot of research and development dollars are being spent adapting GaAs solutions to CMOS processes. For example, BiFET and BiHEMT involve the integration of several functions onto a single die for front-end RF-transceiver modules.

Often, the performance of low-power RF technologies is measured in terms of PA performance metrics and cost benefits. RF switches also should be considered when comparing potential technologies. As a result, developing a cost-effective solution with GaAs-comparable PA performance, digital/analog integration, and fast/linear switches is a must for FDSOI. Being able to offer a complete SoC solution while incorporating RF front-end technology could enable FDSOI to become a significant market player.

Currently, FDSOI resides at the 20-nm node with forecasts from IBS predicting a 14-nm node. The low leakage and relatively low die cost compared to bulk CMOS and FinFETs may make it a more attractive solution for cost-minded mobile-device manufacturers. As modern ICs require multiple voltage conditions for various power options, FDSOI’s ability to offer back-biasing implementations could give it a major advantage in the market. Back-biasing is the ability to adjust the transistors’ threshold voltage conditions. In FDSOI, that is done by tuning the biasing of a buried back gate under the MOSFET channel. According to the “IC Knowledges” study for Siotec, additional fabrication steps of up to 24 mask layers and 60 implants could be required to enable three or four threshold voltages with bulk MOSFETs. These additional steps wouldn’t be required for a back-biased FDSOI device.

This file type includes high resolution graphics and schematics when applicable.

Tuning Considerations

This file type includes high resolution graphics and schematics when applicable.

Another consideration when enabling RF front ends is the ability to tune an antenna efficiently over a wide bandwidth. This could be as wide as 700 MHz to 3.5 GHz to cover all Long Term Evolution (LTE) bands. Such a capability would require highly efficient tuning architectures for impedance matching (or aperture tuning). As the investment in RF SOI leads toward these enhanced features, there has been increased adoption of RF SOI in the handheld market. Yole Development released information indicating that RF SOI switches could be in as many as 65% of handsets already. Clearly, the next big step for RF SOI is to enable a fully integrated front-end module with high-performing power amplifiers (PAs).

Qualcomm and Peregrine will soon be offering single-chip RF solutions utilizing RF SOI technology. Such solutions will include the integration of an RF front end with high-performance digital and analog capability. The goal of these devices is to attract handset manufacturers with a minimally complicated and cost-effective design process. The solutions cover 2G, 3G, 4G, and LTE while offering support for filters, antenna switches, tuners, PA switches, and communications. Qualcomm’s RF front-end solution is a 3D IC stacked configuration, whereas Peregrine’s device comes in die form.

Both Qualcomm and Peregrine require foundries to fabricate their devices, and there are many foundries racing to offer SOI capability. Among those working to provide the foundation for these solutions are GlobalFoundries, IBM, ST, Toshiba, Towerjazz, and Soitec. Yet not all of these solutions are completely incorporating the front end into one module or die. For example, Soitec’s Wave SOI utilizes the firm’s Smart Cut technology to offer high-performance and highly integrated RF front-end modules for SoC applications. According to Soitec, the current product line is compatible with 2G and 3G technologies. The process leverages 70-nmto 1-μm top silicon with a 145-nmto 2-μm buried oxide layer. Control of uniformity is specified at +/-125 angstroms for thin-film technology. Like most SOI offerings, the wafer technology provides wafer resistivity greater than 1 kΩ/cm. Siotec advertises its process as being compatible with standard CMOS processes--operating with power signals, being highly linear, and boasting high RF isolation, low RF loss, and the ability to be integrated digital processes and power management.

The H9SOI FEM RF SOI process from STMicroelectronics offers similar features. ST’s new process is built with MOSFETs on a dual-gate, 0.13-μm and 0.25-μm gate size. Itsupports 1.2-V and 2.5-V MOS and n-type LDMOS (NLDMOS). This could potentially serve higher-power functions for RF front ends. The Ron x Coff characteristics of the current version, according to ST, are 207 fs with potential improvements this quarter leading to 160 fs. According to ST, its NLDMOS with a thick copper layer leads to an additional 10% improvement of efficiency compared to other solutions. The company’s low-noise amplifiers (LNAs) are capable of noise figures of 0.1 dB for GO1 NMOS, which permits a 5-GHz threshold frequency.

IBM reports that its new process, IBM 7RF SOI, offers a mobile-device solution on a single chip that may provide some benefits over GaAs and silicon-on-sapphire (SOS) alternatives. The process is geared toward enabling the latest in LTE and WiFi for mobile devices. The process is manufactured on IBM’s 180-nm SOI technology and has already seen over four billion chips shipped to RF front-end module suppliers. This process offers four metal layers with wirebound glass cut and a core supply voltage of 1.5, 2.5, and 5 V. NFETS and PFETS are compatible with this process. Resistors, capacitors, varactors/diodes, inductors, and electrical fuses are also offered with this process.

Toshiba has launched and is sampling a single-pole, ten-throw RF antenna switch with a MIPI interface for RF front-ends based on SOI technology. The firm claims that its new TaRF5 technology has lower insertion loss and a relatively smaller size compared to other offerings in the smartphone market. Supposedly, its new process achieves improvements of insertion loss up to 25% at 2.7 GHz and a 40% size reduction compared to the TaRF3. Toshiba has been working with SOI-CMOS since 2009 for its smartphone RF antenna switches, which makes it very possible that its new technology boasts other development-knowledge and infrastructure benefits.

Related Articles

• SoCs Bring High-End RF Devices From Lab To Sofa

• LNA Includes Bypass Protection

• Module Boosts WLAN Signals

For its part, TowerJazz offers RF SOI technology focused on efficient RF switches for cellular applications. The company has thick and thin SOI offerings in a variety of voltage levels for either integration or switch figures of merit. In a 3 to 6 metal layer 0.18-μm process, it offers 1.2-, 1.8-, 2.5-, 3.3-, and 5-V options. Channel isolation better than -40 dBm and insertion loss below 0.35 dB is reported for its switch operation. According to TowerJazz, its switches have low harmonics beyond -105 dBc and intermodulation distortion levels below -117 dBm. MOSFETS, BJTS, MIM capacitors, resistors, and varactors are all supported by the process.

Future high-end applications may require more advanced 3D IC approaches. RF SOI may intrinsically lend itself to this technology, as the upper semiconductor layer in a stacked configuration is required to be thin (on the order of less than 100 nm). It is then placed over oxide for isolation. This process already has a place in the development of RF SOI and could lead to multilevel RF SOI stacking and enhanced integration. Because device-scaling approaches may not reduce costs beyond the 28 –nm node, 3D IC development may likely see a significant rise in the near future. RF device companies seem to be embracing SOI as both a current and next-generation solution. The ability to completely incorporate an RF front end into a single chip may be the overriding factor when considering GaAs or Si-based technologies for low-power RF.

This file type includes high resolution graphics and schematics when applicable.

About the Author

Jean-Jacques DeLisle

Jean-Jacques graduated from the Rochester Institute of Technology, where he completed his Master of Science in Electrical Engineering. In his studies, Jean-Jacques focused on Control Systems Design, Mixed-Signal IC Design, and RF Design. His research focus was in smart-sensor platform design for RF connector applications for the telecommunications industry. During his research, Jean-Jacques developed a passion for the field of RF/microwaves and expanded his knowledge by doing R&D for the telecommunications industry.