Cellular-communications evolution has involved increasingly advanced modulation schemes. In the latest-generation (2.5G and 3G) base stations, design strategies include methods for achieving high linearity while also minimizing power consumption. By monitoring and controlling the performance of the base station's power amplifier (PA), for example, it is possible to maximize the PA's output power while achieving optimum linearity and efficiency. Fortunately, the availability of discrete integrated circuits (ICs) tailored for this purpose make it a straightforward matter to monitor and control PA output levels.

The performance of wireless base stations—in terms of power dissipation, linearity, efficiency, and cost— is predominantly determined by the PA in the signal chain. The low cost and high-power performance of silicon laterally diffused metal-oxide-semiconductor (LDMOS) transistors make them well suited for modern cellular base-station PA designs. The inherent trade-offs between linearity, efficiency, and gain determine the optimum bias condition for the LDMOS PA transistor.

For environmental reasons, optimizing a base station's power efficiency is also a key consideration for companies in the telecommunications industry. Significant efforts are being made to reduce the overall energy consumption of base stations to lessen their impact on the environment. The principal day-to-day running cost in a base station is electrical energy. The PA can consume more then one-half of the required power for a base station, so optimizing its power efficiency improves the operational performance and provides environmental and financial benefits.

Controlling the drain bias current to maintain a constant value over temperature and time can significantly improve the overall performance of the PA, while ensuring it stays within regulated output power levels. One method of controlling the gate bias current is to optimize the gate voltage at the test/evaluation stage, fixing it with a resistive divider.

While the fixed gate voltage solution can be cost effective the primary disadvantage is that it does not account for environmental changes, manufacturing spread, or supply voltage variations. Dynamic control of the PA gate voltage using a high-resolution DAC or a lower resolution digital potentiometer offers greater control of the output power. A user-programmable gate voltage allows the PA to maintain its optimized bias condition despite changes in voltage, temperature, and other environmental parameters.

Two principal factors affecting the PA's drain bias current are variations on the PA's high-voltage supply line and on-chip temperature variations. The drain voltage of the PA transistor is susceptible to variation on the high-voltage supply line. Accurate measurement of the current on the high-voltage supply lines using a high-side current (I) sense amplifier makes it possible to monitor the drain voltage of the PA transistor. An external sense resistor (R) sets the full-scale current reading. In applications monitoring very high currents, the sense resistor must be able to dissipate the I2R losses. If the resistor's rated power dissipation is exceeded, its value may drift or it may fail altogether, causing a differential voltage across the terminals in excess of the absolute maximum ratings.

The measured voltage, presented at the output of the current sensor, can be multiplexed into an analog-to-digital converter (ADC) to generate digital data for monitoring purposes. Care should be taken to ensure that the output voltage of the current sensor be as close as possible to the full analog input range of the ADC. Constant monitoring of the high-voltage line enables the power amplifier to readjust its gate voltage when voltage surges are sensed on the line, thereby maintaining an optimum bias condition.

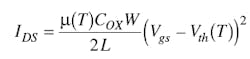

The drain source current of the LDMOS transistor, IDS, has two temperature dependent terms, the effective electron mobility µ and the threshold voltage, Vth:

The threshold voltage and effective electron mobility decrease with rising temperature. Hence, temperature changes will cause variations in output power. Measuring the temperature of the PA using one or more discrete temperature sensors makes it possible to monitor the temperature variations on the board. There are a variety of discrete temperature sensors available to address systems requirements, from analog voltage output temperature sensors to digital output temperature sensors with single-wire, Inter-IC bus (I2C), and Serial Peripheral Inteface (SPI) control.

Multiplexing the voltage presented at the output of the temperature sensor into an ADC allows this temperature data to be converted into digital data for monitoring purposes (Fig. 1). Depending on the system configuration, it may be necessary to use a number of temperature sensors on the board. For example, if more then one PA is being used or a number of pre-drivers are required on the front-end, using a temperature sensor for each amplifier provides more control over the system. In this case, a multichannel ADC is required to convert the analog outputs from the temperature sensors. An internal out-of-range alert function is now commonly featured on a variety of ADCs. This added function flags an alert when the inputs are outside programmed limits. This is valuable for monitoring temperature and current sensor readings in the PA signal chain. Both high- and low limits can be pre-programmed, with alerts being generated only when these limits are violated. Hysteresis registers are also generally featured in such designs. This register type determines the reset point for the alert flag if a limit violation occurs. The hysteresis register prevents a noisy temperature or current sensor reading from continuously toggling the alert flag. Devices such as the models AD7992, AD7994, and AD7998 12-b low-power I2C-interfaced ADCs from Analog Devices (www.analog.com), for example, feature this out-of-range-limit indicator while providing two, four, and eight channels of processing power, respectively.

Using control logic, the digital information gathered from the current sensors and temperature sensors can be continuously monitored. Dynamic control of the PA gate voltage with a digital potentiometer or digital-to-analog converter (DAC)—while monitoring the sensor readings—allows an optimized biased condition to be maintained. The level of control required on the gate voltage will determine the resolution of the DAC. Telecommunications companies commonly use multiple PAs in base-station designs (Fig. 2), since this provides added flexibility in selecting a PA for each RF carrier. Each PA can be optimized toward a particular modulation scheme. Combining parallel PAs also provides improved linearity and overall efficiency. In such cases, the PAs may require multiple cascaded gain stages, including variable-gain amplifiers (VGAs) and predriver stages, to fit the gain and efficiency requirements. A multichannel DAC can accommodate the various level-setting and gain-control requirements of these blocks.

Page Title

To achieve accurate gate control of the PA, DACs such as the models AD5321, AD5627, and AD5625 from Analog Devices offer 12-b, single, dual, and quad outputs, respectively. The parts have excellent source and sink capabilities, which should negate the need for output buffers in most applications. The combination of low power, guaranteed monotonicity, and fast settling time enable accurate level setting applications.

Where precision is not a primary specification, and 8-b resolution is acceptable, a digital potentiometer is a more cost-effective option. These have the same electronic adjustment function as mechanical potentiometers or variable resistors, but provide enhanced resolution, solid-state reliability, and superior temperature performance. Nonvolatile and one-time programmable (OTP) digital potentiometers are ideal in time-division-duplexing (TDD) RF applications where the PA is turned off for the TDD receive period and turned on by a fixed gate voltage for the transmit period. This preprogrammed start-up voltage reduces the turn-on delay and improves efficiency in turning on the PA transistor for the transmit stage. Having the ability to turn off the PA transistor during the receive stage avoids transmit noise corrupting the received signal. This technique also improves the overall efficiency of the PA. Depending on the number of channels, interface type, resolution, and the requirement of nonvolatile memory, a host of digital potentiometers are available for this application. A 256position, one-time programmable, dualchannel, I2C potentiometer such as the model AD5172 from Analog Devices is well-suited for level setting applications in RF amplifiers.

Accurate measurement of the power levels of complex RF signals on the output of the PA allows greater control of the amplifier gain, thus optimizing the efficiency and linearity of the device. Using a root-mean-square (RMS) power detector, allows a precise rms power level to be extracted from the RF signals that can be found in WCDMA, EDGE, and UMTS cellular base stations.

Figure 3 shows a simple control loop with the output of a power detector connected to the gain-control terminal of the PA. Based on the defined relationship between the output voltage, VOUT, and the RF input signal, the power detector will adjust the voltage on VOUT (VOUT is now an error amplifier output) until the level at the RF input corresponds to the applied control voltage, VSET. The ADC completes a feedback loop, which can track the output of the power detector and adjust its VSET input. This method of gain control can be used for the variable-voltage amplifiers (VVAs) and VGAs that are used in preceding stages of the signal chain. To measure both transmit and receive power, dual power detectors are available which simultaneously measure two complex input signals. In a system where a VGA or a predriver amplifier precedes the PA, only one power detector is required. In this case, the gain on one of the devices is fixed, while VOUT feeds the control input of the other.

In situations where voltage spikes or unacceptably high currents are sensed on the high-voltage supply line, the digital control loop may not be fast enough to prevent device damage in certain applications. The digital control loop consists of: sensing the high side current using the current sense, analog-to-digital conversion, and processing the digital data by the external control logic. If the loop determines that the line current is too high, it sends a command to the DAC to reduce the gate voltage or to shut down the part.

An analog comparator can be used to control the RF signal to the PA using an RF switch (Fig. 4). If high current is sensed on the supply line, the RF signal can be switched off to prevent damage to the PA. Using an analog comparator means no digital processing is required, so the control loop is much faster. The output voltage of the current sense can be directly compared to the fixed voltage setup by the DAC. When a voltage higher then the fixed voltage is produced at the output of the current sense, the comparator can toggle a control pin on the RF switch, cutting the RF signal to the gate of the PA almost instantaneously.

A typical PA monitoring and control configuration, using discrete components, is shown in Fig. 5. The only amplifier being monitored and controlled is the PA itself; however, any one of the amplifiers in the signal chain can be addressed in this manner. All the discrete components operate off the same data bus, in this case an I2C databus, and are controlled using one master controller to minimize the parts count, complexity, and cost.

From a design perspective, the key advantage of using discrete components to monitor and control base-station PAs is that it is possible to choose from a selection of custom-fit products. PA vendors are designing increasingly complex PA front-end signal chains that consist of various gain stages and control techniques. Available multichannel ADCs and DACs are ideally suited to address differing cellular base-station system partitions and architectures, thus allowing the base-station designer to implement cost-effective distributed control.