Processor Boasts 3 Billion Transistors on 9 Copper Layers

Integration means many things to many people. But in the world of high-power, high-speed microprocessors, integration means literally billions of transistors on a chip, as researchers from Intel Corp. demonstrated recently. A team led by Reid Riedlinger, Ron Arnold, and Larry Biro (Fort Collins, CO), in addition to Bill Bowhill and associates (Hudson, MA), recently disclosed information on a next generation Intel® Itanium® microprocessor fabricated in a 32-nm silicon CMOS process. The device fits 3.1 billion transistors on a die with 9 layers of copper measuring just 18.2 x 29.9 mm. The processor features 8 multithreaded cores, a ring-based system interface, memory bandwidth to 45 Gb/s, and peak processor-to-processor bandwidth to 128 Gb/s.

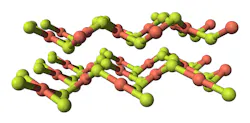

This impressive processor incorporates 54 Mb of on-die cache memory distributed throughout the core and system interface. The device uses high-dielectric-constant metal-gate transistors combined with nine layers of copper interconnections to link the multitude of transistors and passive components. Of the more than 3 billion transistors, 720 million devices are allocated to the eight processor cores. The maximum frequency of the input/output ports and memory interfaces is 6.4 billion transfers per second (GT/s).

The aggregate memory and I/O bandwidths of various ports of the processor easily exceed 115 Gb/s, with several different interfaces operating at transfer rates exceeding 4.8 GT/s per lane with power efficiency of 14 mW per GT/s. The analog portion of the microprocessor includes process-, voltage-, and temperature-tolerant circuitry. See “A 32 nm, 3.1 Billion Transistor, 12 Wide Issue Itanium® Processor for Mission-Critical Servers,” IEEE Journal of Solid-State Circuits, Vol. 47, No. 1, January 2012, p. 177.