Synthesizer Serves MB-OFDM UWB

Jianguo Zhang, Chunhua Wang, Xiaorong Guo, Xin Li, and Guangxiang Zhang

Short-range wireless communications have relied on such standards as Bluetooth and wireless local area networks (WLANs) to move data between points. But ultrawideband (UWB) communications systems also offer practical solutions for short-range data transfers, especially with their high channel capacities and potential data rates. In support of such short-range solutions, a frequency synthesizer was developed for the Federal Communications Commission (FCC) -approved 3.1-to-10-.6-GHz frequency range. With less than 5-ns switching speed and spurious sidebands of less than -47 dBc, it provides outstanding spectral purity for UWB applications. Designed for fabrication with the Taiwan Semiconductor Manufacturing Co.'s (TSMC) 0.18-m silicon CMOS semiconductor process, the frequency synthesizer design draws only 50 mA current from a +1.8-VDC supply.

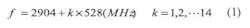

This broadband frequency synthesizer was developed for use in a multiband orthogonal frequency-division-multiplex (MB-OFDM) UWB system. This system divides the frequency range from 3.1 to 10.6 GHz into 14 subbands, each with bandwidth of 528 MHz. These subbands are arranged into five groups.1Figure 1 shows the layout of the frequency spectrum, while Eq. 1 shows how to determine the frequencies of the different subbands:

The band-switching-speed requirements for a MB-OFDM UWB communications system are better than 9.5 ns, requiring fast hopping speed for the frequency synthesizer in such a system. Unwanted sidebands must be suppressed to acceptably low levels as well, making the design of a frequency synthesizer for these systems a difficult challenge.

Frequency synthesizers based on phase-locked-loop (PLL) architectures can be divided into several types. The first type includes more than one PLL.2-4 These sources can meet the switching-speed requirements (less than 9.5 ns) for a MB-OFDM UWB system, although they tend to occupy large die areas and consume large amounts of power. The second type is based on a single PLL.5-7 This type of frequency synthesizer can cover the full required frequency range in a small die area and with low power consumption. They can also achieve high sideband suppression with acceptable frequency switching speed. However, they produce output signals that are susceptible to harmonic pulling and spurious signal generation. Most of this type of synthesizer can over-provide frequency coverage for one or two UWB groups, such as the design of ref. 8. Even when the full frequency range is covered,9,10 more than two single-sideband (SSB) mixers are needed in the synthesizer architecture to generate the required frequency bands.

The proposed frequency synthesizer features a novel architecture comprised of a single PLL, two SSB mixers, and two multiplexers (MUXs). With adequate frequency planning, the synthesizer can generate 14 frequency subbands covering 3.1 to 10.6 GHz. To enhance the performance of the synthesizer, attention was paid to the design of the MUX, SSB mixers, and buffer circuitry. As a result, this synthesizer achieves improved sideband rejection with lower cost and simpler layout than comparable, earlier synthesizer designs.

The architecture of the new UWB synthesizer is shown in Fig. 2. The voltage-controlled oscillator (VCO) generates an 8448-MHz orthogonal signal. Five divide-by-two dividers in the PLL produce in-phase (I) and quadrature (Q) signals at frequencies such as 4224, 2112, 1056, 528, and 264 MHz. The first multiplexer, MUX1, processes the 4224-MHz signal and feeds it to the first single-sideband mixer, SSB1. The local-oscillator (LO) signal for SB1 is obtained from the second multiplexer, MUX2, which selected from the 2112- and 1056-MHz signals. The output of SSB1 feeds the buffer circuit while the output of the buffer is then mixed with the 264-MHz signal in SSB2. All 14 subbands can be obtained from the output of SSB2 as a result of this scheme.

In this frequency synthesizer, spurious signals are caused by nonideal elements in the SSB mixer circuit; the spurs can be suppressed by means of optimizing circuits. For example, the buffer circuit and quality-factor (Q) enhancement circuits in SSB2 yield high sideband suppression. The switching time depends mainly on the response time of the MUXs and SSB mixers. Using only two current-mode logic (CML) MUXs and two SSB mixers results in fast frequency switching time. And using only one PLL, two MUXs, and two SSB mixers saves CMOS die area and power consumption. The MUX1 circuit does not require extra power.

To ensure fast synthesizer switching speed, the MUX must be capable of fast switching time. High third-order harmonic rejection and minimal input-to-output leakage are also key parameters. A CML MUX was selected for its fast switching speed, although this design tends to suffer high input-to-output leakage. To improve upon this performance, a switch-cascode structure11 was employed in the CML MUX. But such a structure is not ideal for two outputs, and a new design was developed, as shown in Fig. 3. One output signal is fed to the input of SSB1; the other is fed to the input of SSB2.

Several transistors are added to the MUX circuit to derive the second output signal, as shown in Fig. 3. The role of transistors M3 and M4, for example, is the same as that of transistors M1 and M2. The output signal from M3 and M4 is controlled by signal S1. If control signals S1 and S4 are enabled, signal OUT2 is selected. Adding M3 and M4 to the circuit has no effect on the input-to-output isolation of the MUX circuit.

Page Title

The phase change produced in the MUX can help to select upconversion or downconversion in the SSB mixer. As shown in Fig. 3, the part on the left side of the line is the same as the part on the right side, except that the output is connected to the opposite side.12 Switching signals S3 and S2 in the MUX change the phase sequences of In1 and help select upconversion or downconversion in the SSB mixer.

As shown in Fig. 3, the activation or deactivation of devices M3 and M4 or M1 and M2 are controlled by S2 and S1 enable and disable functions, respectively. Only one control signal is enabled at one time. Adding transistors M3 and M4 does not consume extra power in the MUX circuit. To counterbalance the gain mismatch, the output impedances of the transistors are changed with the frequencies of the output signals.

Figure 4 shows a the model of the SSB mixer, in which two double-sideband (DSB) mixers are used. The operation of the SSB mixer is given by Eqs. 2 and 3:

which illustrate the mode of upconversion and downconversion of the SSB mixer can be obtained by inversing the phase of signal sinω2t. A traditional Gilbert mixer was employed in the SSB mixer design. The SSB mixer circuit includes an I path and a Q path (Fig. 5). The phase inverse function is implemented by the MUX circuit.

The SSB mixer is a key module in the frequency synthesizer. Usually, the use of a higher number of SSB mixers in a synthesizer design leads to degraded spectral purity. In the SSB mixer circuit, some nonideal factors will impact output spurious performance. For example, phase and gain mismatches at the input port will transform into gain and phase mismatches at the output.12 Two techniques were employed to suppress spurious signals in the synthesizer's outputs. In the first, output impedances were changed with different output signal frequencies, resulting in different output amplitudes. The SSB mixer circuits handle as many as 14 output signals. So, inductive-capacitive (LC) tank circuits with switched capacitor arrays were used to suppress spurious signals.13

To save die area, the SSB mixer was designed with minimal inductance; however, this small inductance can not provide the high Q needed for high sideband spurious rejection. The solution involved adding a negative transconductance (gm) cross-coupled pair in the output of SSB2.14 SSB2 is comprised of a SSB mixer and a negative gm cross-coupled pair. But choosing the value of transconductance is critical to avoid unwanted oscillations. If the sources of transistors M14, M15, and M16 are connected to ground, a change in I3 would result in a change in the output signal. To stabilize the output of SSB2, a tail current (I0) is added, as determined by Eq. 4:

This equation illustrates that the output signal will not change with the changing of current I3. Because the sum of currents I1, I2, and I3 is a fixed value, voltage signal Vout is a constant.

Due to nonlinearities in the SSB mixer, interfering tones and spurious signals are unavoidable at the mixer's output. To minimize spurs at the output of the frequency synthesizer, a second-order LC bandpass filter with switched capacitor arrays15 was employed before the second SSB mixer. The bandpass filter circuit includes a differential pair and a negative-gm cross-coupled pair (Fig. 6). A small-signal equivalent circuit for the filter is shown in Fig. 7.

Ideally, the equivalent resistance of the negative-gm cross-coupled pair and the center frequency can be determined by the following equations:

where:

gm = the transconductance of transistor M3 in Fig. 6 and:

Page Title

The gain of the buffer circuit can be found by Eq. 7:

If transconductance gm→ 2/R, the loss of the LC circuit can be offset by the negative-gm cross-coupled pair, and high Q can also be obtained. According to Eqs. 7 and 8, the gain of the circuit increases as the bandwidth decreases, leading to enhanced output performance for the synthesizer. To avoid oscillation in the buffer circuit, the condition that gm

In addition, if the sources of transistors M5 and M6 are connected to ground (Fig. 6), a change in I1 will yield a change in the output signal. To stabilize the output signal, tail current It is added. Its value can be found by Eq. 9:

The UWB frequency synthesizer was implemented in a commercial silicon CMOS process, the 0.18-m CMOS technology from TSMC. The design achieved better than -35 dBc sideband rejection, and clean output signals, as shown in Fig. 8, Fig. 9, Fig. 10. The phase noise, shown in Fig. 11, is -127 dBc/Hz offset 1 MHz from the carrier. Figure 12 shows the layout of the synthesizer in CMOS. Excluding pads, the active area is only 1.5 x 1.4 mm2. The table provides a comparison of the performance of this novel UWB frequency synthesizer with other reported designs. It features higher sideband rejection, lower cost, and simpler layout. The novel UWB synthesizer can generate all of the 14 subband frequency ranges for a 3.1-to-10.6-GHz MB-OFDM UWB system. It achieves better than 5-ns frequency switching speed with low pbase noise, and consumes only 50 mA current from a +1.8-VDC supply.

Acknowledgment

The authors would like to thank the Open Fund Project of the Key Laboratory in Hunan Universities, Grant No.10K016, for financially supporting this research.

References

- C. Mishra, A. Valdes-Garcia, and F. Bahmani, et al., "Frequency planning and synthesizer architectures for multiband OFDM UWB radios," IEEE Transactions on Microwave Theory and Techniques, Vol. 53, 2005, pp. 3744-3756.

- Che-Fu Liang, Shen-luan Liu, and Yen-Horng Chen, et al., "A 14-Band Frequency Synthesizer For MB-OFDM UWB Application," IEEE International Solid-State Circuits Conference, 2006, Digest of Technical Papers, pp. 428-437.

- Jung-Eun Lee, Eun-Chul Park, and Choong-Yul, et al., "A frequency synthesizer for UWB transceiver in 0.13-m CMOS technology," Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems, 2006, Digest of Papers.

- Marco Gourmand, Eleonora Franchi, and Antonio Gnudi, et al., "A CMOS 90-nm, 55-mW 3.4-to-9.2-GHz 12-band frequency synthesizer for MB-OFDM UWB," IEEE Microwave and Airless Components Letters, Vol. 19, No. 11, 2009.

- Chinmaya Mishra, Alberto Valdes-Garcia, and Edgar Sanchez-Sinencioo, et al., "System and Circuit Design for an MB-OFDM UWB Frequency Synthesizer," IEEE Transactions on Circuits and Systems, Vol. 56, No. 7, July 2009.

- Hui Zheng and Howard C. Luong, Sr., "A 1.5-V, 3.1-8-GHz CMOS Synthesizer for 9-Band MB-OFDM UWB Transceivers," IEEE Journal of Solid-State Circuits, Vol. 42, No. 6, June 2007.

- T. Tokairin, N. Matsuno, and K. Numata, et al., "A 0.18-m CMOS Low-Spurious Local Signal Generator for MB-OFDM UWB Radio," IEEE Radio Frequency Integrated Circuits (RFIC) Symposium, 2007, pp. 215-218.

- Jri Lee and Da-Wei Chiu, "A 7-band 3-8 GHz Frequency Synthesizer with 1-ns band-switching time in 0.18-m CMOS technology," IEEE International Solid-State Circuits Conference, 2005, Digest of Technical Papers, Vol. 1, pp. 204-593.

- Tai-You Lu and Wei-Zen Chen, et al., "A 3-10-GHz, 14-Band CMOS Frequency Synthesizer with Spur Reduction for MB-OFDM UWB System," IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2011, pp 1-11.

- Tai-You Lu and Wei-Zen Chen, "A 3-to-10-GHz, 14-Band CMOS Frequency Synthesizer with Spur Reduction for MB-OFDM UWB System," IEEE International Solid-State Circuits Conference, 2005, pp. 197-200.

- Che-Fu Liang and Shen-luan Liu, "A Fast-Switching Frequency Synthesizer for UWB Application," Asian Solid-State Circuits Conference, 2006, Digest of Technical Papers, pp. 428-437.

- Danfeng Chen, Haipeng Fu, and Yunfeng Chen, et al., "A sideband-suppressed low-power synthesizer for 14-band dual-carrier MB-OFDM UWB transceivers," IEEE International Synposium on Circuits and Systems (ISCAS), 2010, pp. 2139-2192.

- Hong Zhang, Yangyang Niu, and Shengdong Tang, et al., "A 3.1-10.6-GHz Frequency Synthesizer for MB-OFDM UWB Transceivers," 2010 International Symposium on Signals Systems and Electronics, Vol. 1, 2010, pp. 1-4.

- Chao-Shiun Wang, Wei-Chang Li, and Chomg-kuang Wang, et al., "A 3-10 GHz full-band single VCO agile switching frequency generator for MB-OFDM UWB," IEEE Asian Solid-State Circuits Conference, 2007, pp. 75-78.

- F. Dulger, E. Sanchez-Sinencio, and J. Silva-Martinez, et al., "A 2.1-GHz, 1.3-V, 5-mW programmable Q-enhancement LC bandpass biquad in 0.35-m CMOS," Proceedings of the IEEE 2002 Custom Integrated Circuit Conference, 2002, pp. 283-286.

- Hyun-Su Chae, Eun-Chul Park, and Choong-Yul Cha, et al., "A Fast Hopping Frequency Synthesizer for UWB Systems in a CMOS Technology," Second International Symposium on Wireless Communication Systems, 2005, pp. 370374.