According to Keysight Technologies, its DDR Bus Simulator is the first to generate accurate bit-error-rate (BER) contours for the JEDEC double-data-rate (DDR) memory bus specification. Statistical simulation speeds up calculation of DQ and DSQ eye probability density distributions and BER contours for memory interfaces. This eliminates the need for time-consuming bit patterns.

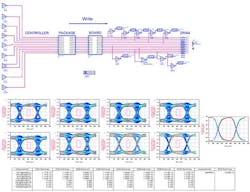

Previous tools constructed eye diagrams using precarious dual-Dirac extrapolation of a limited bit pattern from either a SPICE-like or convolutional channel simulation. The DDR Bus Simulator, however, constructs the eye diagram from the transmitter, channel, and receiver impulse responses, and from the stochastic properties of a conceptually infinite non-repeating bit pattern. It accounts for crosstalk and asymmetry between rising and falling transition times, as well as provides comprehensive timing and voltage margins between the contour and DDR4 receive mask specification.

Available as a new option for Advanced Design System (ADS) 2014.11, the simulator allows for three IC model types: built-in, IBIS, or circuit models—all of which can be mixed and matched in a schematic. An additional DDR Bus Simulator Distributed Computing 8-pack enables users to farm out their parameter sweeps to a compute cluster for a shorter time-to-answer.

Keysight Technologies, 5301 Stevens Creek Blvd., Santa Clara, CA 95051; (877) 424-4536