Power-amplifier (PA) design, especially for wireless communications systems, often involves the trade-off between linearity and efficiency. Fortunately, modern computer-aided-engineering (CAE) tools can help to decide on the best approach to making such trade-offs quickly and efficiently.

As an example, consider some requirements for a PA. For this project, these requirements include RF output power level of 50 W peak envelope power (PEP) at 760 MHz with input drive level of 1 W, output load impedance of 50 Ω, efficiency of 50 percent, and bias voltage of +28 VDC. The transistor selected for this amplifier is a model MRF9045M LDMOS device from Freescale Semiconductor (Tucson, AZ).

A possible starting point for the PA design is the selection of the active device bias point. The DC drain current (IDS) level should allow the amplifier to meet the efficiency requirement while also providing the necessary output power and linearity. With no experience in using this device, selecting a bias point can seem challenging. Start by drawing a load line along with the IV curves for the transistor.1 Point IQ in Fig. 1 seems to be an appropriate point at this early stage in the design process, and the value can always be changed when a CAE simulation tool is available for analysis.

In many designs, biasing FET devices can be accomplished by providing a bias voltage directly to the gate through an appropriate impedance. This impedance must be sufficiently high at the frequency of operation to avoid RF power from reaching the DC supply. The bias circuitry must also present an impedance that prevents the device from becoming unstable up to the gain-bandwidth (FT) of the device. An S-parameter test can be performed to verify the bias circuit stability by placing the termination ports of the simulation at the bias points (e.g., VGG and VDD) and terminating the amplifier's input and output ports with appropriate values (e.g., 50 Ω).

Part of the PA design process involves the addition of matching circuits. The amplifier should remain stable even as input and output impedances are changed.

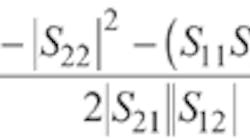

A stable circuit is defined as having a bounded response for a bounded input. The Rollett Stability factor (K) is typically used in PA design to quantify stability. The definition of K is based on s-parameters:

where values of K greater than unity (K > 1) are required for a stable two-port network.1,2

The initial design includes capacitors C1, C2, C11, and C14 (Fig. 2) with negligible impedance at the frequency of interest and used for DC blocking or AC decoupling. Transmission-line TL1 (a quarter wave at the design frequency) and inductor L1 provide RF isolation for the bias circuitry, while resistors R1 and R2 and capacitor C3 are added for stability.

Figure 3 offers an S-parameter simulation results for this design. Since K is greater than 1 at the operating frequency, the design appears stable. At this point, a large-signal analysis has not been performed since the matching circuits needed for the desired output power have not yet been included in the design.

To maximize output power; the transistor must be presented with a certain impedance at both the load and source ports. Typically a designer will perform a load-pull analysis to determine a target load impedance. Simulated load-pull results on this initial design predict maximum PAE of 50.51 percent and maximum power delivered of +44.45 dBm. Load-pull analysis is useful in that it clearly shows on the Smith Chart what the target load impedance should be.

Since the maximum predicted output power for this design is +44.45 dBm at the optimum load, rather than the target +47 dBm, the design might be considered less than satisfactory. But the load-pull analysis was not performed at the optimum input impedance for the amplifier. Rather a value of 1 Ω was selected initially as a starting point based on the transistor's specifications. By performing a source-pull analysis, a better value of input impedance can be found. The improved results of this analysis (not shown), of 57.12 percent for PAE and +45.98 dBm for maximum power delivered, still fall short of the design goal for power. At this point with a hardware-only design, the input impedance would be set to an optimum source match and the load-pull measurement would be repeated, with repeated iterations between load-pull and source-pull analyses until no further improvements are possible. At that point, hopefully, the design requirements would be met. With CAE software, the process can be carried out much more efficiently with an optimization technique that aids in finding optimum component values for the design targets.

Based on the load-pull and source-pull analyses, matching circuits were designed and added to the original PA design, and harmonic-balance simulation was used to study the effects on output power, PAE, gain compression, and AM-to-PM conversion. The simulated output power and PAE are lower than what was expected from the source-pull results. This is due to the use of realistic component models (i.e., not ideal) for the matching circuits. These results show the importance of having accurate models even for passive components. The output-power results (+45.58 dBm or about 36 W) with the nominal input power of 30 dBm is still below the target of 50 W, the PAE is close to the requirement. Although no requirements were set for the PA's linearity performance, it currently stands at 1.8 dB of compression at the nominal input power.

The use of simulation tools with optimization capability helps eliminate repetitive analyses and specify requirements as goals. An optimizer changes specified component values until performance requirements are met or until it has reached a maximum number of specified trials. For the PA design, several optimization goals were established: that amplifier fundamental output power be greater than +47 dBm and that second harmonics be better than –40 dBc (so that harmonic products do not get out of control). More requirements could be added as needed as long as they are realistic for the particular topology and for the components being used.

In this optimization, only the microstrip transmission line lengths for the matching circuits and the RF drain isolation were varied, although other components (such as the capacitors in the matching circuits) could have been included. However, the parameters being optimized (output power and second harmonics) were not sensitive to the capacitors mainly because these are part of a vendor library with fixed increments. The transmission line lengths, on the other hand, were varied in a continuous manner. Nonetheless, it was found that some of the values for the transmission lines were not as sensitive anyway (e.g., TL10 changed from 250 mil to 246.5 mils) and could have been taken out of the optimization.

The modified PA design after optimization is show in Fig. 4, with simulated performance in Fig. 5. Not only were the design goals met, but the optimization kept the compression performance under control by lowering the overall compression by 1 dB at the nominal input power. Once the simulated goals have been met, the amplifier must be built and tested, ideally with real-world modulated signals. Of course, it would also be useful to simulate performance with the same type of signals. Using an integrated CAE tool that allows the designer to co-simulate digitally modulated carriers along with the analog/RF circuit (i.e., mixed signal analysis) would surely reduce the gap between design and test. For example, Fig. 6 shows the PA being fed by a 16QAM signal. Two analyses were performed: one with nominal carrier input power of +30 dBm and one with a 5-dB backoff. The higher power spectrum shows the higher sideband power due to the higher drive level causing stronger nonlinear effects. Results also show the ideal 16QAM constellation and the distorted constellation for the higher output power signal.

Other Digital Communication analyses are also possible, such as Error Vector Magnitude (EVM). The EVM versus Output Power results are shown in Fig. 7. In this analysis it was not enough to determine the EVM as the carrier power was swept, we had to determine the output modulated signal power.

When an amplifier must be analyzed with a known modulation format such as EDGE, a CAE tool with integrated standards can save a great deal of simulation setup time. Close links between the simulation software and test equipment, such as the Agilent 89600 vector signal generator, can help in testing completed hardware when other parts of a design are still being modeled or virtual. In Fig. 8 we show the output of the simulator being analyzed by the same software used for the vector signal analyzer. This capability can also be used to run analyses with some parts of the hardware already available while the rest is still a virtual design.

In short, the power and utility of high-frequency CAE simulation tools can bring obvious benefits to the design cycle, as shown here for this 50-W PA. Entire design flows can be integrated using CAE tools. Capability such as mixed signal analysis with real Analog/RF components and modulated signals will provide invaluable information both at the circuit and system integration design levels.

REFERENCES

- Steve Cripps, RF Power Amplifiers for Wireless Communications, Artech House, Norwood, MA, 1999.

- G. Gonzalez, Microwave Transistor Amplifiers Analysis and Design, Prentice Hall, Upper Saddle River, NJ, 1997.

- Andy Howard, Load Pull Simulation Using ADS, white paper, Agilent Technologies, Santa Rosa, CA, www.agilent.com.

- ADS2004A manual - http://eesof.tm.agilent.com/.