Sichun Du, Chunhua Wang, and Guangxiang Zhang

Ultrawideband (UWB) communications offers the potential of high-speed data transfers across short distances at low power levels. But before the technology can be practically implemented, a variety of building-block components, including low-cost amplifiers, will be needed. By applying a standard 0.18-m silicon CMOS process, a 3.1-to-10.6-GHz UWB low-noise amplifier (LNA) was designed and fabricated. It features current-reuse technology for low-power dissipation and flat gain with frequency. This broadband amplifier achieves 16.5-dB voltage gain with 1 dB gain flatness and excellent input match (with S11 of less than 10 dB) across its 7500-GHz operating bandwidth. It also offers low noise figure, with performance of 2.8 dB, and operates with extremely low power consumption, requiring only 6 mW power from a +1-VDC supply.

In February 2002, the United States Federal Communications Commission (FCC) approved the First Report and Order (R&O) for the unlicensed commercial use of UWB technology under strict power emission limits; the International Telecommunications Union Radiocommunications Sector (ITU-R) has also championed the use of this technology for high-data-rate, short-range wireless communications. The low-power technology is ideal for wireless local area networks (WLANs) and various other in-home wireless applications.1 Because of its potential for high-data-rate communications at low power levels over short distances, the number or researchers paying attention to the technology have increased dramatically in recent years.

The FCC and ITU-R both define UWB as a transmission with a signal bandwidth of the lesser of 500 MHz or 20% of the center frequency. Two modulation approaches are vying for acceptance by the IEEE 802.15.3, a committee that supports standardization of UWB communications technology: multiband orthogonal-frequency-division-multiple (MB-OFDM) and direct-sequence UWB (DS-UWB) technology. No matter which of these standards is finally endorsed, the LNA will be an essential component in the construction of future UWB communications receivers and systems.

Compared to applications in narrowband systems, the requirements for designing an LNA are far more stringent when the amplifier will be used in broadband and UWB applications. Such an amplifier must have good input impedance matching, high gain that remains flat with frequency from 3.1 to 10.6 GHz, low noise figure across this broad bandwidth, good linearity, and relatively low power consumption.

A number of different circuit topologies have been applied in recent years to the development of UBB LNAs, including distributed amplifiers,2 common-gate amplifiers,3 circuits with resistive shunt feedback,4 and amplifiers employing current-reuse techniques.5 Due to the large die area and high power consumption, distributed-amplifier topologies are not well suited for use in UWB LNAs. Common-gate amplifiers may provide the best topology for achieving the good input match needed by an UWB LNA, but the noise figure of this type of amplifier is somewhat higher than the other approaches, and the gain is not particularly flat with frequency.6 An LNA based on a feedback configuration can achieve the wideband performance needed in an UWB LNA, but because of the presence of parasitic capacitance in the amplifier transistor, this configuration is limited for applications at higher frequencies.7

The current-reuse topology may provide the best combination of high power gain, low noise figure, and low power consumption, making it a viable candidate for use in UWB LNA designs. In an amplifier employing current-reuse techniques, the input RF signal is amplified by two cascaded common-source amplifier stages to provide high gain. At the same time, this topology also supports low noise figures. The input matching circuitry is aided by a highpass filter to suppress noise. To explore the possibility of applying current-reuse techniques to the design of an UWB LNA, Cadence Spectre RF circuit design software from Cadence Design Systems was used to design the amplifier, which was then fabricated in a standard silicon 0.18-m RF CMOS semiconductor process. Figure 1 shows a schematic diagram with the key circuit elements for the experimental CMOS UWB LNA. The circuit includes an input matching stage, main amplifier stage, and output buffer stage. The input matching network is formed by transistor M1 and inductors L1 and L2. In this circuit, M1 also serves the role of first-stage amplifier. By means of inductor L4, the load of the first amplifier stage is made resonant with the input capacitance of the second stage. The second amplifier stage is boosted by transistor M2, providing good high-frequency gain. The output buffer stage is bolstered by transistor M3. Capacitors Cdc1 and Cdc2 are DC blocking capacitors, while capacitor C1 is a coupling capacitor and C2 is a bypass capacitor.

The value of C2 was chosen to be as large as possible to provide an ideal AC ground, as in conventional narrowband LNA designs.8 In addition, the value of inductor L3 is sufficiently large in the desired frequency band to provide a high-impedance path to block unwanted signals. As a result, the input RF signal can be amplified twice under this structure. A series peaking technique is used with the load formed by inductor L5 and resistor R2 to extend the frequency response of the amplifier. Inductor L6 is used for interstage matching and for further bandwidth extension.

The current-reuse technique is well known for its use in LNAs, for its capability of achieving high performance with power consumption that is less than conventional two-stage common-source amplifiers Fig. 2(a)>. In such a design approach, transistors M1 and M2 are connected as a cascade structure by means of coupling capacitor C1; load inductor Lload and load resistor Rload are the loads for transistors M1 and M2; and currents ID1 and ID2 are the drain currents for transistors M1 and M2.

Figure 2(b) shows the schematic diagram for the two-stage current-reuse common-source amplifier, with C2 used as a bypass capacitor. By comparing Figs. 2(a) and 2(b), it can be seen that currents ID1 and ID2 can be reused as current ID; there is just one current path between drain voltage Vdd and ground. In the experimental current-reuse LNA, the amplifier topology has been transformed from a two-stage common source structure without changing the essential amplifier type, resulting in high gain without adding power consumption.

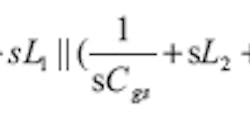

As shown in Fig. 3, the input matching network is composed of capacitor Cdc1, gate-source capacitor Cgs for transistor M1, inductors L1 and L2, with Rload the resistance seen looking from the input impedance matching stage to the next amplifier stage. This network yielded a low input in-band reflection coefficient across the UWB frequency range. In addition, the highpass filter within this circuitry, composed of Cdc1 and L1, provides excellent noise suppression. The combination provides a good low-end frequency cutoff and excellent wideband characteristics. Figure 4 shows a simplified small-signal equivalent circuit of the input matching network.

As Fig. 3 shows, Cgs is the parasitic gate-to-source capacitance and L2 is a source degeneration inductor. For simplicity's sake, all other parasitic effects are ignored. As a result, the input impedance can be derived by means of Eq. 1:

When the amplifier's key parameters are carefully tuned, it is possible to achieve input impedance matching and noise matching at the same time.

The experimental current-reuse-based LNA employs an internal common-source configuration with two stages. The voltage gain of a common-source amplifier can be found by means of Eq. 2:

where:

r0 = the output resistance of transistor M1 and

RL = the load resistance.

Page Title

From Fig. 1, it is possible to develop the simplified equivalent-circuit small-signal-gain amplifier topology shown in Fig. 5. This circuit can be divided into two parts, with the voltage gain of the first part, Av1, found from the relationship shown in Eq. 3:

The voltage gain of the second part of the amplifier circuit of Fig. 5, Av2, can be found by applying Eq. 4:

With these two separate voltage gains, the voltage gain of total circuit can be derived as shown in Eq. 5:

The use of current-reuse and inductive series peaking techniques contribute to high gain and excellent gain flatness in the experimental LNA. In addition, inductor L6 was inserted between the amplifier stage and buffer stage to further extend the LNA's bandwidth. One of the key performance parameters in the design of any LNA is noise figure which, in general, sets the noise figure for the first stage of a receiver. Noise figure is additive in an LNA, depending on the number of stages, with the noise of the first stage having the greatest impact on the overall noise figure of a multistage amplifier. The total noise figure of a multistage LNA circuit configuration, Ftotal, can be found from Eq. 6:

where:

F1 = the noise figure of the amplifier's first stage and

G1 = its gain.

Obviously, keeping the noise figure of the first stage low makes it possible to achieve a low overall noise figure for a multistage LNA. In the experimental UWB LNA, two methods were applied to improve the noise performance. One involves the use of the simplified highpass input matching network mentioned earlier; this highpass filter has just one spiral inductor for simplicity and to reduce the noise associated with the parasitic resistances of additional inductors. Low noise figure is also aided by the current-reuse LNA configuration. Since it consists of a two-stage cascaded common-source amplifier (from Eq. 6), it can be seen that the noise figure of second stagewhich is produced by transistor M2 and inductors L4 and L3can be reduced by boosting the gain of the first stage. Similarly, the noise figure contributed by the buffer stage and the load stage can also be reduced by increasing the gain of the first and second stages. This design approach has made it possible to achieve high gain and low noise figure simultaneously.

Figure 6, Figure 7, Figure 8, and Figure 9 offer plots of simulated performance for the UWB LNA design produced by the SpectreRF circuit simulation software from Cadence. A supply voltage of +1 VDC was assumed in these simulations, with power consumption of only 6 mW projected as a result. Figure 6 shows simulated results for input reflection coefficients (S11). The simulated S11 performance is lower than -10.0 dB over the full 3.1-to-10.6-GHz UWB frequency range. Figure 7 shows simulated results for the UWB LNA's output reflection coefficient (S22). These simulated performance levels are better than -10.5 dB across the full UWB frequency range.

These simulated results for S11 and S22 indicate good input and output impedance matching for the UWB LNA. Figure 8 reveals that the simulated noise figure is about 2.8 to 4.2 dB over the frequency band from 3.1 through 10.6 GHz, with a minimum value of 2.8 dB at 4 GHz. Figure 9 shows that the simulated forward voltage gain for the UWB LNA is about 15.5 to 17.5 dB across the full UWB frequency range from 3.1 to 10.6 GHz. When fabricated with standard silicon CMOS, the UWB LNA chip layout (Fig. 10) measures about 1.50 x 1.50 mm. The table shows the simulated performance of the experimental LNA compared with prior work.

Acknowledgments

The authors would like to thank the Science and Technology Planning Project of Hunan Province No. 2010FJ4246 and The Fundamental Research Funds for The Central Universities for financially supporting this research.

References

- Faranak Nekoogar, Ultra-Wideband Communications: Fundamentals and Applications, Prentice-Hall, New York, 2005.

- Ming-Da Tsai, Kun-You Lin, and Huei Wang, "A 5.4-mW LNA Using 0.35-m SiGe BiCMOS Technology for 3.1-10.6-GHz UWB Wireless Receivers," IEEE Radio Frequency Integrated Circuits Symposium, 2005.

- Yuna Shim, Chang-Wan Kim, Jeongseon Lee, and Sang-Gug Lee, "Design of Full Band UWB Common-Gate LNA," IEEE Microwave and Wireless Components Letters, Vol. 17, No. 10, October 2007.

- Ruey-Lue Wang, Min-Chuan Lin, Chih-Cheng Lin, and Cheng-Fu Yang, "A 1-V Full-Band Cascoded UWB LNA with Resistive Feedback," RFIT2007-IEEE International Workshop on Radio-Frequency Integration Technology, December 9-11, 2007.

- Zhe-Yang Huang, Che-Cheng Huang, Yeh-Tai Hung, and Meng-Ping Chen, "A CMOS Current Reused Low-Noise Amplifier for Ultra-Wideband Wireless Receiver," Microwave and Millimeter Wave Technology, 2008.

- Z. D. Huang, Z. M. Lin, and H.C. Lai, "A High Gain Low Noise Amplifier with Current-Reused Technique for UWB Applications," Electron Devices and Solid-State Circuits, 2007.

- C.W. Kim, et al., "An Ultra-Wideband CMOS Low Noise Amplifier for 3-5-GHz UWB System," IEEE Journal of Solid State Circuits, Vol. 40, No. 2, February 2005, pp. 544-547.

- H.L. Kao, Albert Chin, K.C. Chang, and S. P. McAlister, "A Low-Power Current-Reuse LNA for Ultra-Wideband Wireless Receivers from 3.1 to 10.6 GHz," IEEE Conference On Silicon Monolithic Integrated Circuits in RF Systems, 2007 Topical Meeting on Digital Object Identifier, 2007.

- Chia-Chien Li and Jeng-Rern Yang, "Noise improvement of 3-5-GHz CMOS UWB LNA With Low power consumption," 2010 Asia-Pacific International Symposium on Electromagnetic Compatibility, April 12-16, 2010.